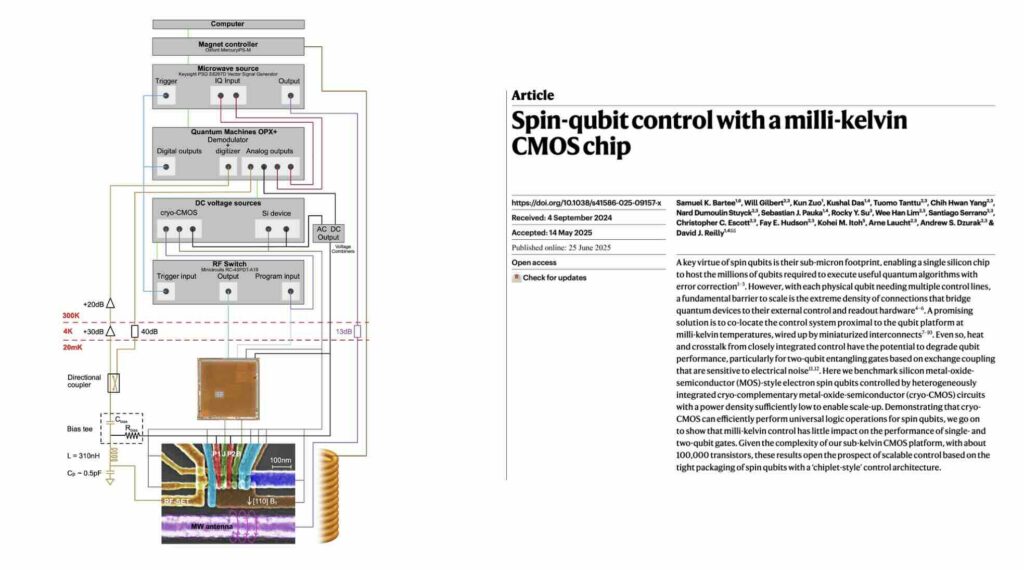

在朝着实用化量子计算迈进的路上,硬件控制系统一直是最难以突破的瓶颈之一。近期《Nature》发表的一项研究《Spin-qubit control with a milli-kelvin CMOS chip》,由澳大利亚悉尼大学、Diraq公司以及Keio大学等机构联合完成,首次展示了一个可在毫开尔文温度下运行的低功耗CMOS控制芯片,成功地与硅基自旋量子比特集成,实现了单量子比特与双量子比特逻辑门操作。这项研究不仅验证了“芯粒式”(chiplet-style)集成架构的可行性,也为高密度、低热干扰的量子芯片设计提供了新的方案。

然而,这项成果在引发兴奋的同时,也揭示出量子计算在“工程可行”与“商用实用”之间仍存巨大鸿沟。我们必须承认,量子计算即便取得了这一类硬件上的突破,距离成为具备经济性、稳定性与通用性的市场技术仍遥遥无期。它更可能在未来几十年内,继续作为前沿科研与技术展示的代表存在,而非变成真正普及的通用计算平台。

微尺度操控的挑战

当下主流的量子计算平台大多仍处于几十到上百个物理量子比特的规模,距离完成有实用意义的纠错容错计算——通常需要数百万个比特——还有几个数量级的差距。即便以自旋量子比特的微小尺寸计算,控制问题依然棘手。每个比特至少需要数根控制线,连接至室温的脉冲与读出设备。线路密度、热负载、信号串扰,共同构成了当前系统扩展性的“物理边界”。

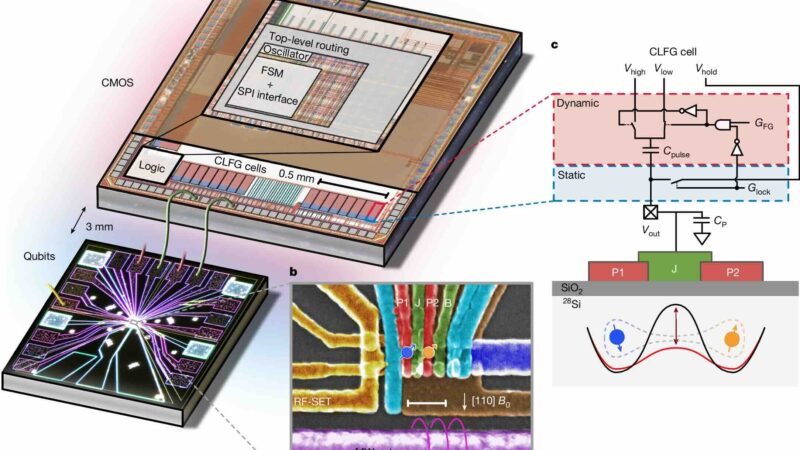

本研究采用一种异构集成策略,将一个约含10万个晶体管的CMOS芯片,直接与量子芯片置于同一个毫开尔文冷台上,并通过微型互连线进行连接,从而有效减少控制路径长度、降低热负载和线缆密度。

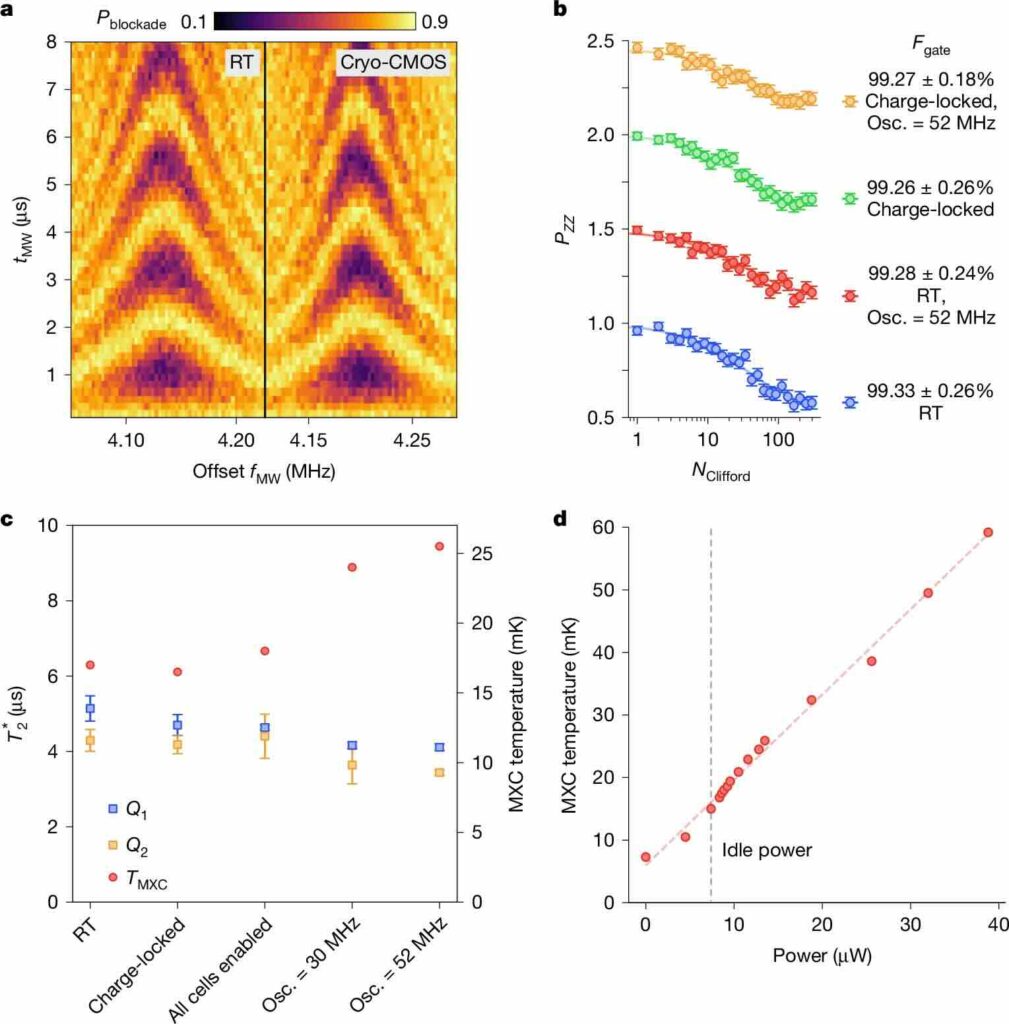

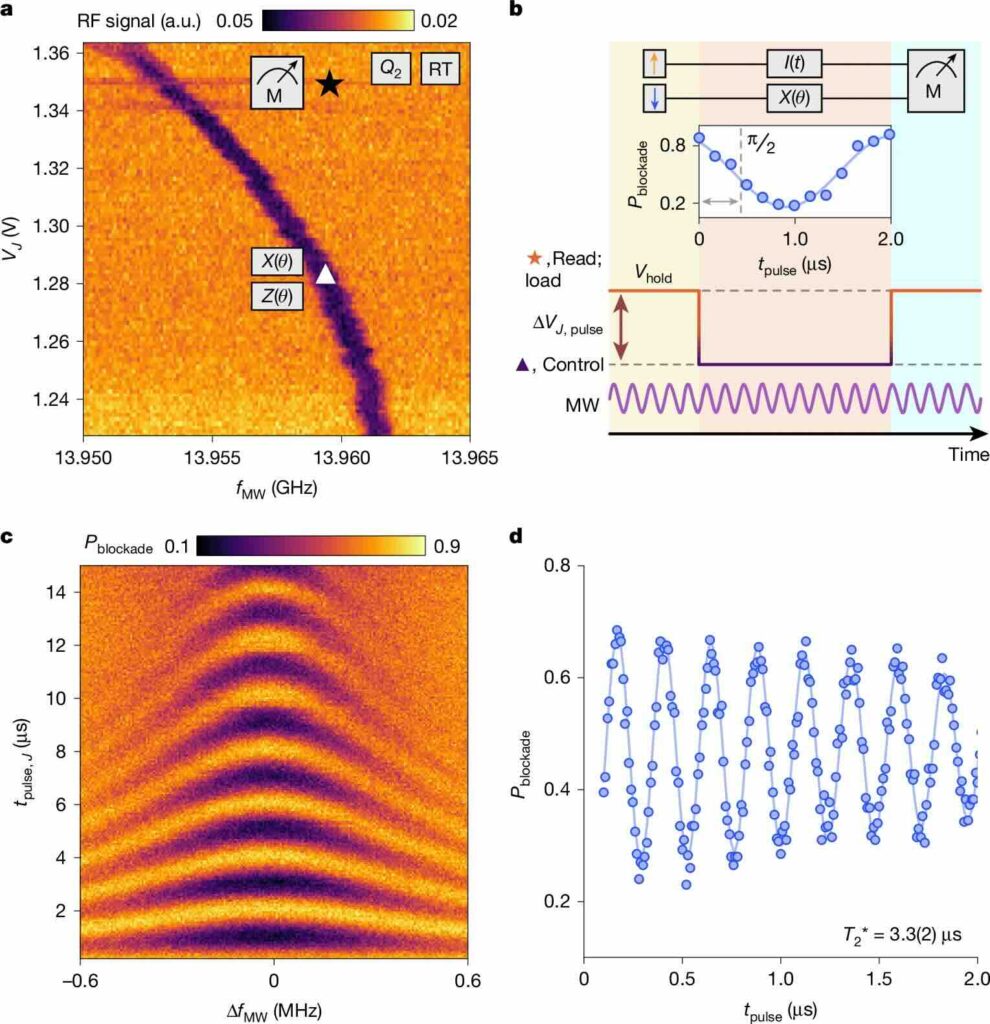

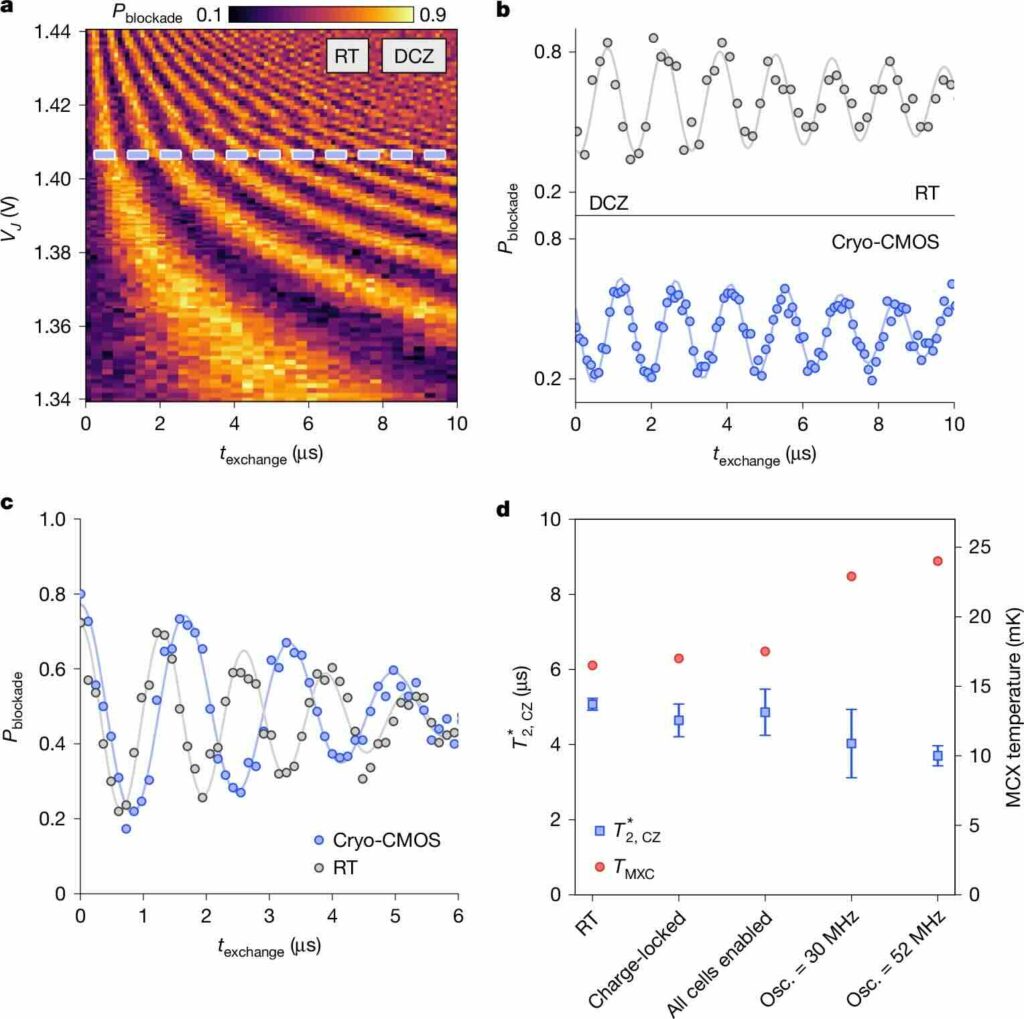

在实验中,研究团队使用28nm FDSOI(完全耗尽型硅绝缘体)工艺制造的CMOS芯片,实现了对硅量子点中单电子自旋的操控,包括Rabi振荡、Ramsey干涉、Hahn回波以及随机门基准测试(RBM)。双量子比特门则基于可调节的交换耦合(Heisenberg exchange),实现了受控Z门(CZ)。实验结果表明,CMOS控制方案带来的量子门保真度与传统室温电子设备相当,保真度下降不超过0.1%。

热量不是问题?串扰也许尚可控

将晶体管放入毫开尔文环境听上去是个疯狂的主意,但该研究表明:低功耗设计、静态电压锁定与分时激活等策略,使得芯片功耗维持在纳瓦/兆赫兹的量级,在1毫瓦冷却预算下完全可行。文中指出,在极低频率(例如30MHz)下,32个门控通道在全激活状态下对系统温度几乎无影响;即使在52MHz频率下,温度上升也非常有限,且对相干时间的影响可忽略不计。

值得注意的是,实验未观察到显著的电气串扰。研究者分析认为,电路的低温运行压制了热噪声,同时“电荷锁定”机制在门控操作之间将CMOS与量子比特电气解耦,仅保留最小的电容耦合路径。这种策略使得系统运行期间大部分时间处于低扰动状态,达到了软硬件协同降噪的目的。

现实距离:从原型到实用,还需多少步?

尽管该工作令人印象深刻,但它仍只是一个“可行性原型”:仅控制两个量子比特、依赖外部室温触发与时序逻辑、整体系统仍需精密稀释制冷设备配合。离实用、稳定、成本可控的“量子计算模块”还有极远距离。

更重要的是,即便控制系统得以微型化和冷却优化,量子计算自身的门保真度与容错机制也仍未成熟。目前最强的纠错码如表面码(Surface Code)需要99.9%以上的门操作精度,而该研究中的最高值约为99.3%,这仍意味着无法大规模叠加逻辑比特。

此外,文章中的“芯粒式架构”虽然在热与串扰上提供了解决思路,但也引入了新问题——芯片间通信与布局复杂度。如何在成百上千个量子控制模块之间同步协调,尚无统一工程路径可依。

技术进步的价值不止于商业

量子计算很可能不是下一个“互联网”或“人工智能”。至少在当前,我们必须接受它仍是一种科研导向技术,其进展更多代表人类在极限物理与工程控制能力上的突破。

正如本文所述的毫开尔文CMOS芯片,它不仅是工程上的杰作,也为未来低温电子学与新型探测技术提供了借鉴。即便最终未能大规模商用,它也可能为诸如精密测量、模拟物理、材料探索等领域开辟新天地。

当我们评估量子计算的未来时,应当既不盲目乐观,也不因“商业不确定性”否定它的科学意义。毕竟,许多最伟大的技术进展,都曾在一开始被误判为“无用的科研玩具”。但是有一点我们必须要清醒,在本世纪内,我们或许仍将看到量子计算停留在“科幻”与“科研”之间。